- 您现在的位置:买卖IC网 > Sheet目录528 > UPA2755AGR-E2-AT (Renesas Electronics America)MOSFET N-CH DUAL 30V 8-SOIC

�� ��

��

��

��DATA� SHEET�

�MOS� FIELD� EFFECT� TRANSISTOR�

�μ� PA2755AGR�

�SWITCHING�

�N-CHANNEL� POWER� MOS� FET�

�DESCRIPTION�

�The� μ� PA2755AGR� is� Dual� N-channel� MOS� Field� Effect�

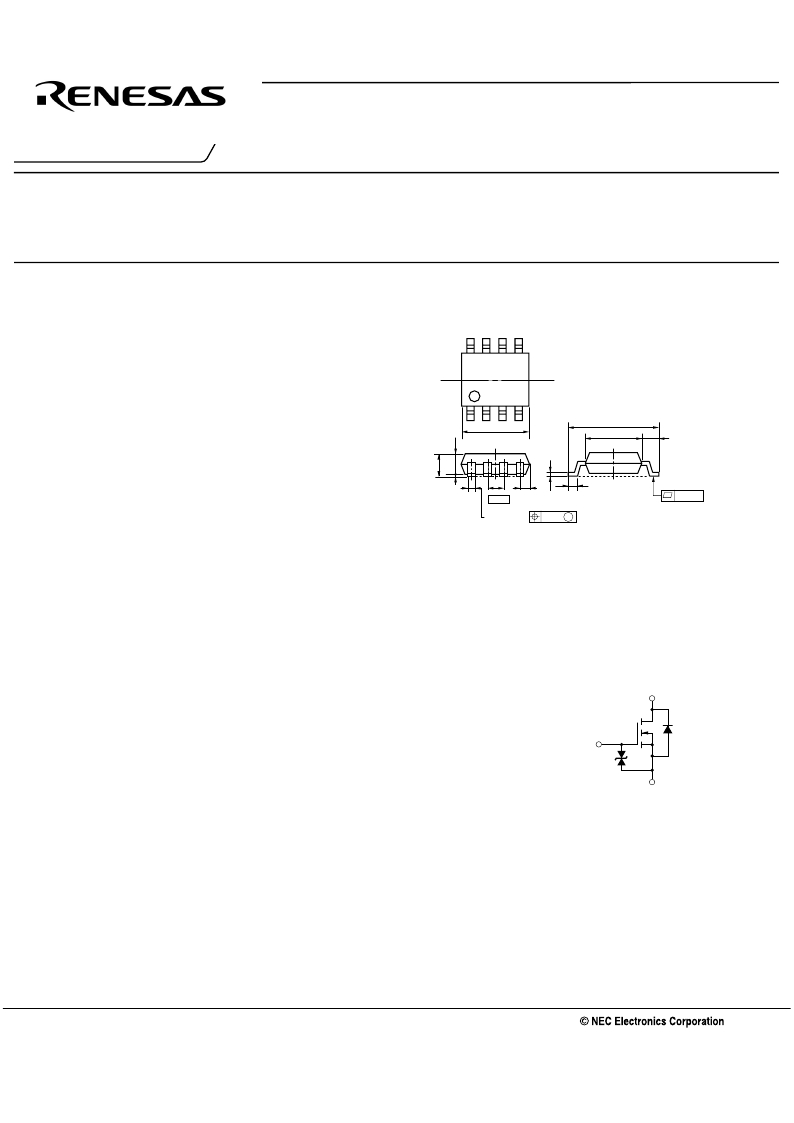

�PACKAGE� DRAWING� (Unit:� mm)�

�Transistor� designed� for� DC/DC� converters� and� power�

�management� applications� of� notebook� computers.�

�FEATURES�

�8�

�5�

�1� :� Source� 1�

�2� :� Gate� 1�

�7,� 8:� Drain� 1�

�3� :� Source� 2�

�4� :� Gate� 2�

�5,� 6:� Drain� 2�

�?� Dual� chip� type�

�?� Low� on-state� resistance�

�1�

�5.37� MAX.�

�4�

�6.0� ±0.3�

�4.4�

�0.8�

�R� DS(on)1� =� 18� m� Ω� MAX.� (V� GS� =� 10� V,� I� D� =� 4.0� A)�

�R� DS(on)2� =� 29� m� Ω� MAX.� (V� GS� =� 4.5� V,� I� D� =� 4.0� A)�

�?� Low� input� capacitance�

�1.27� 0.78� MAX.�

�0.5� ±0.2�

�0.10�

�C� iss� =� 650� pF� TYP.�

�0.40�

�+0.10�

�–0.05�

�0.12� M�

�?� Built-in� G-S� protection� diode�

�?� Small� and� surface� mount� package� (Power� SOP8)�

�ABSOLUTE� MAXIMUM� RATINGS� (T� A� =� 25� °� C,� All� terminals� are� connected.)�

�Drain� to� Source� Voltage� (V� GS� =� 0� V)�

�V� DSS�

�30�

�V�

�Drain� Current� (pulse)�

�Gate� to� Source� Voltage� (V� DS� =� 0� V)�

�Drain� Current� (DC)� (T� C� =� 25� °� C)�

�Note1�

�V� GSS�

�I� D(DC)�

�I� D(pulse)�

�±� 20�

�±� 8.0�

�±� 32�

�V�

�A�

�A�

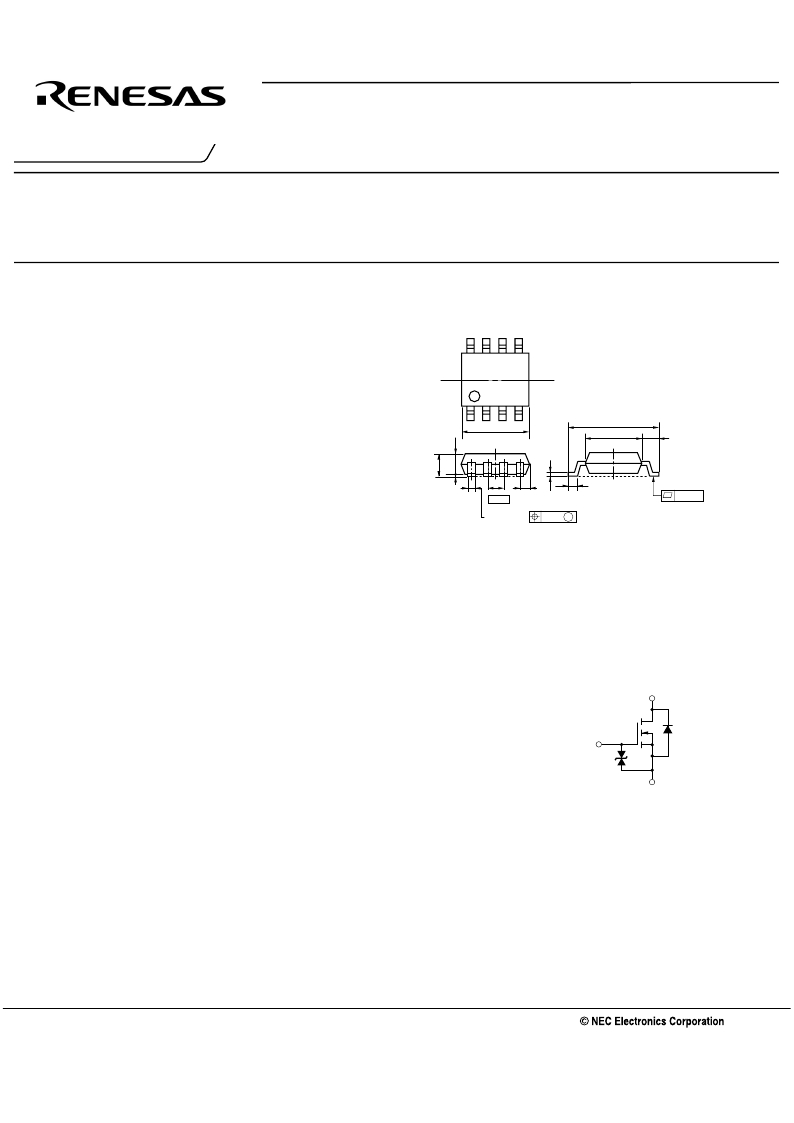

�EQUIVALENT� CIRCUIT�

�(1/2� circuit)�

�Total� Power� Dissipation� (1� unit)�

�Note2�

�P� T�

�1.7�

�W�

�Drain�

�Total� Power� Dissipation� (2� units)�

�Note2�

�P� T�

�2.0�

�W�

�Channel� Temperature�

�Storage� Temperature�

�Single� Avalanche� Current�

�Note3�

�T� ch�

�T� stg�

�I� AS�

�150�

�?� 55� to� +150�

�8�

�°� C�

�°� C�

�A�

�Gate�

�Body�

�Diode�

�Single� Avalanche� Energy�

�Note3�

�E� AS�

�6.4�

�mJ�

�Gate�

�Protection�

�Diode�

�Source�

�2.� Mounted� on� ceramic� substrate� of� 2000� mm� x� 2.2� mm�

�Notes� 1.� PW� ≤� 10� μ� s,� Duty� Cycle� ≤� 1%�

�2�

�3.� Starting� T� ch� =� 25� °� C,� V� DD� =� 15� V,� R� G� =� 25� Ω� ,� V� GS� =� 20� →� 0� V�

�Remark� The� diode� connected� between� the� gate� and� source� of� the� transistor� serves� as� a� protector� against� ESD.�

�When� this� device� actually� used,� an� additional� protection� circuit� is� externally� required� if� a� voltage� exceeding�

�the� rated� voltage� may� be� applied� to� this� device.�

�The� information� in� this� document� is� subject� to� change� without� notice.� Before� using� this� document,� please�

�confirm� that� this� is� the� latest� version.�

�Not� all� products� and/or� types� are� available� in� every� country.� Please� check� with� an� NEC� Electronics�

�sales� representative� for� availability� and� additional� information.�

�Document� No.� G19282EJ1V0DS00� (1st� edition)�

�Date� Published� May� 2008� NS�

�Printed� in� Japan�

�2008�

�发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

UPA2756GR-E2-AT

MOSFET N-CH DUAL 60V 8-SOIC

UPA2757GR-E2-AT

MOSFET N-CH DUAL 30V 8-SOIC

UPA2790GR-E2-AT

MOSFET N/P-CH 30V 8-SOIC

UPA2791GR-E2-AT

MOSFET N/P-CH 30V 8-SOIC

UPA602T-T1-A

MOSFET N-CH DUAL 50V SC-59

UPA603T-T2-A

MOSFET P-CH DUAL 50V SC-59

UPA606T-T2-A

MOSFET N-CH DUAL 50V SC-59

UPA607T-T1-A

MOSFET P-CH DUAL 50V SC-59

相关代理商/技术参数

UPA2755GR

制造商:NEC 制造商全称:NEC 功能描述:SWITCHING N-CHANNEL POWER MOSFET

UPA2755GR-A1-E2-A

制造商:Renesas Electronics Corporation 功能描述:

UPA2755GR-E1-A

制造商:Renesas Electronics Corporation 功能描述:

UPA2755GR-E1-AZ

制造商:Renesas Electronics Corporation 功能描述:

UPA2756GR

制造商:NEC 制造商全称:NEC 功能描述:SWITCHING N-CHANNEL POWER MOSFET

UPA2756GR-E1

制造商:Renesas Electronics Corporation 功能描述:

UPA2756GR-E1-AT

功能描述:MOSFET N-CH DUAL 60V 8-SOIC RoHS:是 类别:分离式半导体产品 >> FET - 阵列 系列:- 产品目录绘图:8-SOIC Mosfet Package 标准包装:1 系列:- FET 型:2 个 N 沟道(双) FET 特点:逻辑电平门 漏极至源极电压(Vdss):60V 电流 - 连续漏极(Id) @ 25° C:3A 开态Rds(最大)@ Id, Vgs @ 25° C:75 毫欧 @ 4.6A,10V Id 时的 Vgs(th)(最大):3V @ 250µA 闸电荷(Qg) @ Vgs:20nC @ 10V 输入电容 (Ciss) @ Vds:- 功率 - 最大:1.4W 安装类型:表面贴装 封装/外壳:PowerPAK? SO-8 供应商设备封装:PowerPAK? SO-8 包装:Digi-Reel® 产品目录页面:1664 (CN2011-ZH PDF) 其它名称:SI7948DP-T1-GE3DKR

UPA2756GR-E2-AT

功能描述:MOSFET N-CH DUAL 60V 8-SOIC RoHS:是 类别:分离式半导体产品 >> FET - 阵列 系列:- 产品目录绘图:8-SOIC Mosfet Package 标准包装:1 系列:- FET 型:2 个 N 沟道(双) FET 特点:逻辑电平门 漏极至源极电压(Vdss):60V 电流 - 连续漏极(Id) @ 25° C:3A 开态Rds(最大)@ Id, Vgs @ 25° C:75 毫欧 @ 4.6A,10V Id 时的 Vgs(th)(最大):3V @ 250µA 闸电荷(Qg) @ Vgs:20nC @ 10V 输入电容 (Ciss) @ Vds:- 功率 - 最大:1.4W 安装类型:表面贴装 封装/外壳:PowerPAK? SO-8 供应商设备封装:PowerPAK? SO-8 包装:Digi-Reel® 产品目录页面:1664 (CN2011-ZH PDF) 其它名称:SI7948DP-T1-GE3DKR